HyperLynx DRC performs Design Rule Checks on boards for EMI/EMC issues, as well as Signal Integrity and Power Integrity. It is highly customizable, allowing users to create DRCs for practically anything.

### **Overview**

HyperLynx DRC is a powerful, fast design rule checking tool that is fully customizable. It allows for verification of complex design rules that are not easily simulated, such as rules for EMI/EMC. With 23 standard Design Rule Checks (DRCs) for items such as traces crossing splits, reference plane changes, shielding and via checks, you can quickly and easily pinpoint trouble spots on your board that can cause issues with EMI/EMC, Signal Integrity, and Power Integrity.

#### **FEATURES AND BENEFITS:**

- 23 built-in checks for EMI/EMC, SI, and PI issues

- Advanced geometric engine for powerful and efficient design rule checking

- Easy setup and navigation with Setup Wizard and Project Explorer

- Complete custom DRC creation environment

- Built-in script debugger with geometry visualization

- Ability to access layout data and GUI, and manipulate and measure geometries of layout data in custom DRCs

HyperLynx DRC accesses database objects through the Automation Object Model, or AOM, and allows for advanced geometrical operations on these objects. This gives you unique access to the design database and allows you to develop many types of DRCs. With support for VBScript and JavaScript, as well as thorough documentation of the AOM and DRC coding standards, and a built-in script debugging environment, you can be writing your own DRCs immediately.

#### **Custom Rule Creation**

With HyperLynx DRC, you can write custom Design Rule Checks (DRCs) which can then be run in the HyperLynx DRC by yourself and others. HyperLynx DRC contains a complete custom DRC creation environment, including a script debugger with geometry visualization.

When writing custom DRCs, you can access all aspects of the layout, including stackup, layers, planes, traces, vias, pins, and TieLegs. These objects are all part of the Automation Object Model (AOM) library, which is extensively documented. The library contains the building blocks of any custom DRC. Additionally, you have access to electrical models such as IBIS. You can use custom DRCs to perform logical actions on design geometries, such as AND, OR, and XOR. Additionally, you can manipulate and measure the desired geometries of a design when performing a check.

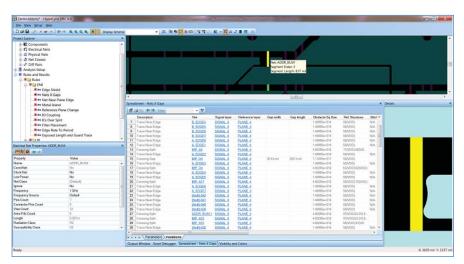

### **Script Writing and Debugging Environment**

HyperLynx DRC features a complete script writing and debugging environment. Built into the GUI is a script debugger, which allows you to set break points, walk through the script step by step, and add variables to a watch list. Variables on the watch list can be a variety of data, including numbers as well as geometries being operated upon by the script, which can be visualized in the board viewer in the GUI.

The script debugging environment allows you to visualize geometries being accessed by the script as you are working on your custom DRC.

## **Easy Setup and Navigation**

The HyperLynx DRC GUI is designed for quick and easy access to design data. A built-in Setup Wizard walks you through the setup to run design checks on your board. Items such as electrical model assignment, connector definition, power/ground net definition, discrete components, and electrical net definition are all in the Setup Wizard. If you are using an Xpedition design, most of this information is already set up in Constraint Manager and transferred during the export to HyperLynx DRC. You can

review all aspects of the design using Project Explorer, which provides the navigation for the HyperLynx DRC GUI.

#### 23 Built-In DRCs

HyperLynx DRC includes 23 standard Design Rule Checks (DRCs) which check for items related to electromagnetic interference (EMI), Signal Integrity (SI), and Power Integrity (PI). Many of the checks look for items that cannot be easily simulated, such as traces crossing splits, reference plane changes, shielding and via checks. The checks can be used to perform a comprehensive review of a board design, and eliminate problems.

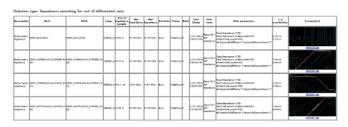

### **Error Reports**

You can select errors from the violation listing for viewing in HyperLynx DRC. In addition, Sharelist reports (containing the image, violation details and coordinates) can be generated in HTML format for broader team review.

| 5 | 3 h ← →           | Filter             | - V             | ShareList Differential_Impedance + |          | R di                    |               |

|---|-------------------|--------------------|-----------------|------------------------------------|----------|-------------------------|---------------|

|   | Description       | Rule name          | Net I           | Net2                               | Layer    | Out of impedance Length | Min Impedance |

| 1 | Below target ing. | Rues/SI/Diff In.   | TOTAL CONTROL   |                                    | SEMALE   | 573.7 mil               | 197.94 Ohm    |

| 2 | Below target inc. | Rules/SI/Diff In.  | DOES OUR HIGH   | DESCRIPTION                        | SIENALS  | 3.251 W                 | 87.94 Okm     |

| 1 | Below target inc. | Rules/SI/Ditt Inc. | DORG LOWER DA   | DORG LOWER DA                      | SIENAL 4 | 3515 in                 | 87.94 Ohm     |

| 4 | Above target on   | Pulso/SI/Dell Inc. | DDR2 LOWER DA   | DORS LOWER DA                      | SENAL 4  | 227.1 mil               | 1107 Ohn      |

| 5 | Below target inp. | Fules/SI/Ort In.   | DORG LIPPER DAT | DORU UPPER DAT                     | SIGNAL 4 | 3.105 in 1              | 83.94 Ohm.    |

|   | Above target im   | Rules/SI/Diff In.  | DOR2 CLK HI[0]  | DOR2 CLK LO[0]                     | SIGNAL 4 | 142.E mil               | 110.7 Ohm:    |

| 7 | Below target imp. | Rules/SI/Diff In.  | DOR2 CLK HI[6]  | DOR2 CLK LO[0]                     | SIGNAL 4 | 3.275 in                | 87.94 Chm     |

| 1 | Above target im.  | Pules/5I/Diff In.  | DOR? CLK HE(II) | DDR2 CLK LO[0]                     | SIGNAL S | 30 mil                  | 110.7 Ohm     |

|   | Above target in   | Rules/SI/Diff In.  | DORS CLK HEST   | DDR2 CLK LO[3]                     | SIGNAL 4 | 166.5 mil               | 110.7 Ohrs    |

# **Supported PCB layout systems:**

- Mentor PADS® Layout, Xpedition® and Board Station®

- Cadence Allegro, SPECCTRA and OrCAD Layout

- Zuken CADStar, Visula and CR3000/5000 PWS or Board Designer

#### For the latest product information, call us or visit: www.mentor.com/hyperlynx

©2014 Mentor Graphics Corporation, all rights reserved. This document contains information that is proprietary to Mentor Graphics Corporation and may be duplicated in whole or in part by the original recipient for internal business purposes only, provided that this entire notice appears in all copies. In accepting this document, the recipient agrees to make every reasonable effort to prevent unauthorized use of this information. All trademarks mentioned in this document are the trademarks of their respective owners.

Corporate Headquarters Mentor Graphics Corporation 8005 SW Boeckman Road Wilsonville, OR 97070-7777 Phone: 503.685.7000 Fax: 503.685.1204

Sales and Product Information Phone: 800.547.3000 sales\_info@mentor.com Silicon Valley Mentor Graphics Corporation 46871 Bayside Parkway Fremont, CA 94538 USA Phone: 510.354.7400 Fax: 510.354.7467

North American Support Center Phone: 800.547.4303 Europe Mentor Graphics Deutschland GmbH Arnulfstrasse 201 80634 Munich Germany Phone: +49.89.57096.00 Fax: +49.89.57096.400 Pacific Rim Mentor Graphics (Taiwan) 11F, No. 120, Section 2, Gongdao 5th Road

Gongdao 5th Road HsinChu City 300, Taiwan, ROC Phone: 886.3.513.1000 Fax: 886.3.573.4734 Japan Mentor Graphics Japan Co., Ltd. Gotenyama Garden 7-35, Kita-Shinagawa 4-chome

7-35, Kita-Shinagawa 4-chome Shinagawa-Ku, Tokyo 140-0001 Japan

Phone: +81.3.5488.3033 Fax: +81.3.5488.3004

MF 9-14

11030620-w